AUIインターフェースに100G×16を追加すれば、標準化が早まる?

この結果、続く7月のミーティングにおいてObjectiveが改定されたほか、前回の最後で少しだけ触れた、OSFP-XDを利用した「頭の悪いソリューション」が早速提案されたのはさすがに笑えた。提案者はVIAVI solutionsのPaul Brooks氏とHuaweiのXinyuan Wang氏である。

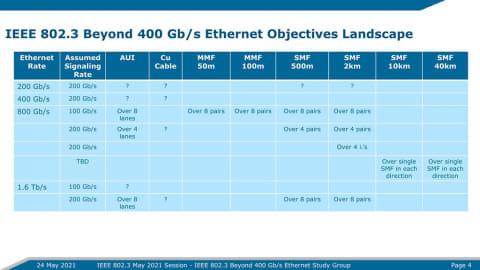

両氏の提案は、要するにAUIインターフェースに100G×16を追加すれば標準化が早まる、というものだ。過去の歴史で言えば、1つのEthernet規格に複数のAUIオプションが含まれるのは普通であり、例えば800Gにしても100G×8と200G×4があるのだから、1.6Tは100G×16と200G×8があってもいいはずだ、というわけだ。

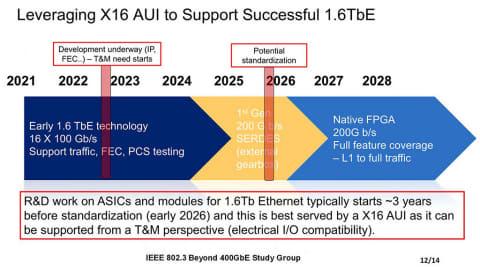

1.6Tb/sに関する仕様が追加されたほか、ちょこちょこ変更がある。出典は"Project Documentation Revisited - IEEE 802.3 Beyond 400 Gb/s Ethernet Study Group Electronic July 2021 Session"そもそも、AUIに200Gレーンが実現できるのはいつになるかを、過去のCMOSロードマップから推定すると、2026~2027年になるとされている。いずれは200Gに移行するとしても、そこまでの間は100Gレーンでつないでもいいだろう、と氏は主張している。

筋から言えば、200G×8と400G×4という気もしなくはないが、200Gですら四苦八苦している現状で、400G×4なんてオプションが用意できるはずがないのも自明だプロセスノードで言えば3ないし2.1nm(これはTSMCのプロセスノードが前提だと思われる)あたりで200Gが可能になると見ており、3nmは早ければ2022年末から2023年初頭に可能となるが、2nmは2024~2025年あたりとみられる(この世代、TSMCもGAAFETを導入する関係で、どこまでスムーズに行くかはっきりしない)また、100G×16の場合、早期にテストツールの着手に取り掛かれることもメリットとしている。

当たり前だが、ベンダー各社は標準化が完了すれば(可能ならその前に)、これに準拠する製品をリリースしたいと考えている。こうした先端製品の場合、企画から製品化まで2年ほどということも珍しくない。

もちろんここでASICを起こすとなると、1~2年余分に掛かるが、テスト用の機材や第1世代の製品の場合、FPGAベースでの開発は珍しくなく、これだとTape out(物理的な配置配線を含む設計完了)後、即量産に入れることになる。問題は、そのFPGAが200Gに対応するのは相当先、ということだ。

実際は、SerDes以外にもさまざまな要素が絡むが、いずれにしても現行のFPGAでは足りないことだけははっきりしている。次世代製品の投入時期も、現状では不明なままだ既にテスト機器メーカーは200G/Lane世代を見据えたテスト機器の開発に着手しているのだろうが、これが現実に提供できるのは相当先になりそうだこの手の先端製品という意味では、Xilinxの「Virtex/Versal」シリーズや、Intel(旧Altera)の「Stratix/Agilex」シリーズになるが、XilinxのVersal PremiumにしてもIntelのAgilexにしても、現状搭載されている汎用高速SerDesはNRZで58G(PAM4で112G、Agilexだと116G)が最大速度であり、200Gに対応する製品は存在しない。

となると、FPGAの外部に何らかの方法で1:2のGearboxを入れるしかなく、これを用意するまで開発も検証も止まることになる。ところが、先に触れたOSFP-XDが利用できるとなれば、100G×16が現実的に可能になる、というわけだ。

もちろん、16レーンのAUIとなれば、これをまたがるFECを用意する必要があるので、手直しが不要というわけではない。ただが、これに要するコストはわずかで、実現可能性は高い、としている。

OSFP-XDの実現可能性をまずチェックすべきだと個人的には思うが、OSFP内部での作業でもあり外からは伺い知れない。というか参考文献がLightwave Onlineというあたりが……200/400G Ethernetで16レーンという仕様は既に存在しているから、この延長だと言えばその通りなのだが……そして、100Gb/sレーンが利用可能なら、少なくともAUIに関して言えば既に開発を始められる(対応したFPGAが存在する)ので、さまざまなコンポーネントやテスト機器の開発を開始できることになる。

さらに、プロセスの微細化が進行すれば2025年頃からは200Gb/sレーンへの対応が始められると予測され、2027年頃にはこれを利用した200Gb/sレーンの製品が出荷できる見通しだ。

100Gレーンベースの測定機器(T&M:Test & Measurement)が先行すれば、これを200Gにするのはそう難しくないというのも、その通りだこれが通ったら、なし崩しにSMF×16の仕様も追加されそう……これは、1.6T Ethernetの早期の立ち上げにつながることになり、決して悪い話ではない。ということで、1.6Tb/s EthernetのAUIに16レーン構成を追加する、というプロポーザルでプレゼンテーションを終わっているのだが、これはあくまでもAUI、つまり機器とモジュール(またはモジュール内部)のみの仕様であり、光インターフェースの方は考慮されていない。

現行の200Gb/s×8レーンという構成を前提にすれば、モジュール内部には2:1のGearboxを入れないといけないわけだ。そのGearboxの測定器はどうする? という話になりそうだ。そのあたりを含めると、言っていることは理解できるものの、やっぱり「頭の悪いソリューション」な感じは拭えない。いや、これにあわせてSMF×16とかの仕様が定まるなら、それはそれで辻褄は合うのだが。